- •1. Вычислительный цикл процессора.

- •2. Вентили и логические элементы.

- •3. Понятие архитектуры и микроархитектуры. Классификация вычислительных средств по архитектуре (классификация Флинна).

- •4. Микропроцессор (мп). Состав и основные функции. Процессоры risc и cisc.

- •5. Архитектура ia-32. Режимы работы процессора.

- •6. Архитектура ia-32. Особенности представления информации.

- •7. Архитектура ia-32. Регистры общего назначения и сегментные регистры.

- •8. Архитектура ia-32. Регистры смещений и регистр флагов.

- •9. Архитектура ia-32. Организация памяти.

- •10. Архитектура ia-32. Организация прерываний.

- •11. Ассемблер. Области применения. Достоинства и недостатки.

- •12. Ассемблер. Структура программы. Модель памяти small.

- •13. Ассемблер. Основные типы предложений.

- •14. Ассемблер. Описание сегмента данных.

- •15. Ассемблер. Способы адресации памяти.

- •16. Ассемблер. Команды пересылки данных. Арифметические команды

- •17. Ассемблер. Команды переходов. Процедуры.

- •18. Ассемблер. Команды управления циклами. Команды прерывания.

- •19. Запоминающие устройства. Иерархичная организация памяти. Основные показатели быстродействия системы памяти.

- •20. Физические основы работы внутренней памяти. Энергозависимая память.

- •21. Внутренняя энергонезависимая память.

- •22. Аппаратно-программные методы ускорения обработки данных. Распараллеливание операции

- •23. Аппаратно-программные методы ускорения обработки данных. Кэширование памяти.

- •24. Кэш прямого отображения. Наборно-ассоциативный и ассоциативный кэш.

- •25. Микроархитектурные особенности процессоров x86 I-V поколений.

- •26. Микроархитектурные особенности процессоров x86 VI поколений.

- •27. Микроархитектура NetBurst и Intel Core.

- •28. Архитектура ia-64.

1. Вычислительный цикл процессора.

Функционирование процессоров в основном состоит из повторяющихся рабочих циклов, каждый из которых соответствует выполнению одной команды программы. Завершив рабочий цикл для текущей команды, процессор переходит к выполнению рабочего цикла для следующей команды программы.

В общем виде команды, выполняемые процессором, имеют следующий формат:

|

КОП |

Аk |

КОП - код операции, затребованной в команде, Аk - адресный код.

В зависимости от того, сколько полей содержит адресный код различают команды: безадресные, одноадресные, двухадресные и т.д.

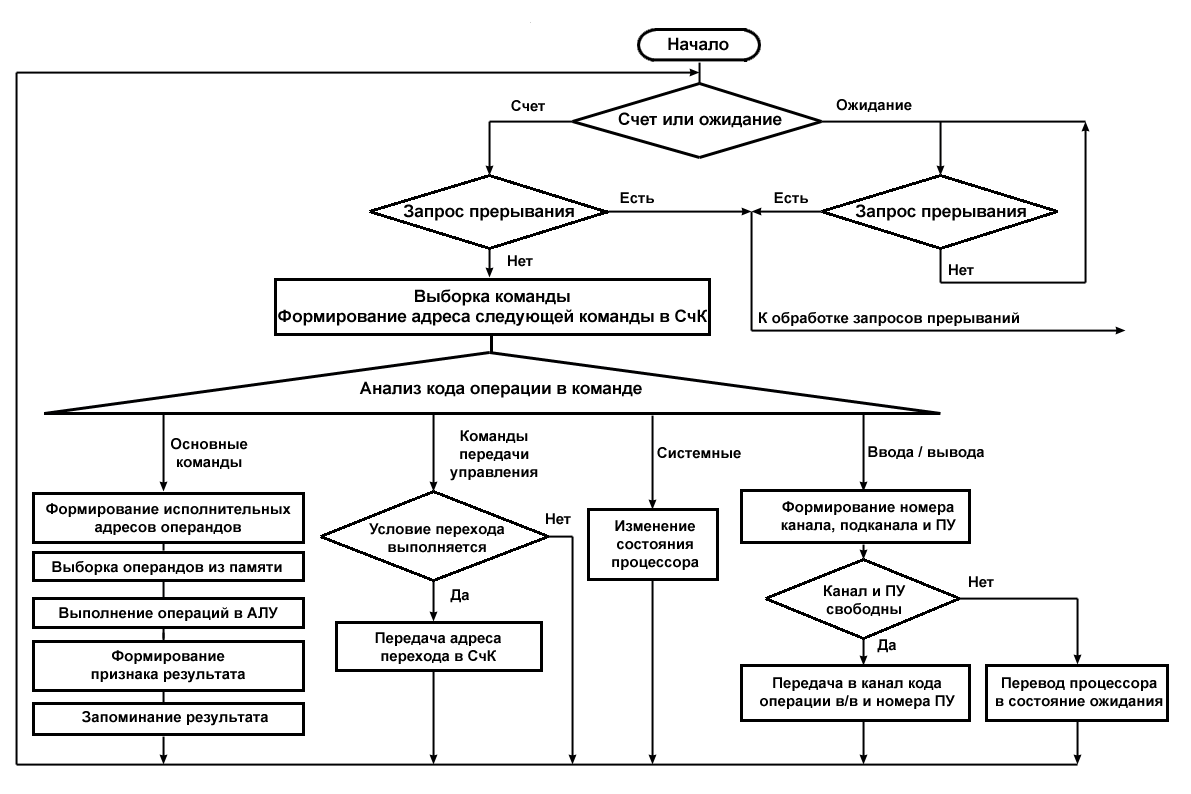

Схема рабочего цикла процессора представлена на рисунке 1.4.

На схеме показаны варианты рабочего цикла для четырех групп команд:

-

основных (арифметические, логические и пересылочные операции)

-

передачи управления

-

ввода-вывода

-

системных (устанавливающих состояние процессора, маску прерывания, слово состояния программы и др.)

Рабочий

цикл начинается с распознавания состояния

процессора - "счет" или "ожидание".

Далее производится проверка наличия

немаскированных прерываний.

В состоянии "ожидание" никакие программы не выполняются - процессор ждет поступления прерывания, после чего управление передается прерывающей программе, переводящей процессор в состояние "счет".

Рисунок 1.4. Рабочий цикл процессора

В состоянии "счет" при наличии немаскированных прерываний происходит выход из нормального рабочего цикла и переход к процедуре обработки запросов прерывания.

При отсутствии прерываний в состоянии "счет" последовательно выполняются этапы рабочего цикла: выборка очередной команды и определение по коду операции ее группы, подготовка операндов (формирование исполнительных адресов и выборка операндов из памяти), обработка операндов в АЛУ и запоминание результата.

На этапе выборки очередной команды образуется согласно естественному порядку адрес следующей за ней команды (продвинутый адрес), при этом счетчик команд инкрементируется.

В процессе выполнения заданной командой операции формируется признак результата операции, используемый командами условного перехода при организации ветвлений в программах.

Указанная выше последовательность составляет основной вариант рабочего цикла, реализуемый при выполнении основных команд.

При выполнении команд передачи управления проверяется заданное условие. Если условие не выполняется, то следующую команду указывает продвинутый адрес, установленный ранее в СчК. Если условие выполняется, то в СчК передается адрес, заданный командой передачи управления.

Команды ввода-вывода инициируют в канале операцию обмена информацией между ядром ЭВМ (основной памятью) и периферийным устройством.

Системные команды осуществляют переключения состояния процессора (программы) путем загрузки нового слова в регистр состояния процессора.

2. Вентили и логические элементы.

В основе построения компьютеров, а точнее аппаратного обеспечения, лежат так называемые вентили. Они представляют собой достаточно простые элементы, которые можно комбинировать между собой, создавая тем самым различные схемы. Одни схемы подходят для осуществления арифметических операций, а на основе других строят различную память ЭВМ.

Вентель - это устройство, которое выдает результат булевой операции от введенных в него данных (сигналов).

Простейший вентиль представляет собой транзисторный инвертор, который преобразует низкое напряжение в высокое или наоборот (высокое в низкое). Это можно представить как преобразование логического нуля в логическую единицу или наоборот. Т.е. получаем вентиль НЕ.

Соединив пару транзисторов различным способом, получают вентили ИЛИ-НЕ и И-НЕ. Эти вентили принимают уже не один, а два и более входных сигнала. Выходной сигнал всегда один и зависит (выдает высокое или низкое напряжение) от входных сигналов. В случае вентиля ИЛИ-НЕ получить высокое напряжение (логическую единицу) можно только при условии низкого напряжении на всех входах. В случае вентиля И-НЕ все наоборот: логический нуль получается, если все входные сигналы будут единицами. Как видно, это обратно таким привычным логическим операциям как И и ИЛИ. Однако обычно используются вентили И-НЕ и ИЛИ-НЕ, т.к. их реализация проще: И-НЕ и ИЛИ-НЕ реализуются двумя транзисторами, тогда как логические И и ИЛИ тремя.

Выходной сигнал вентиля можно выражать как функцию от входных.

Транзистору требуется очень мало времени для переключения из одного состояния в другое (время переключения оценивается в наносекундах). И в этом одно из существенных преимуществ схем, построенных на их основе.