книги / Практическая цифровая схемотехника

..pdfМинистерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования «Пермский национальный исследовательский политехнический университет»

С.Ф. Тюрин

ПРАКТИЧЕСКАЯ ЦИФРОВАЯ СХЕМОТЕХНИКА

Утверждено Редакционно-издательским советом университета

в качестве учебного пособия

Издательство Пермского национального исследовательского

политехнического университета

2020

1

УДК 681.32

Т89

Рецензенты:

кандидат физико-математических наук,

доцент А.С. Епифанов

(Институт точной механики и проблем управления РАН, г. Саратов);

доктор технических наук, доцент В.И. Фрейман (Пермский национальный исследовательский политехнический университет)

Т89 Тюрин, С.Ф.

Практическая цифровая схемотехника : учеб. пособие / C.Ф. Тюрин. – Пермь: Изд-во Перм. нац. исслед. политехн. ун-та, 2020. – 55 с.

ISBN 978-5-398-02397-8

Изложен материал практикума по цифровой схемотехнике, отсутствующий в других учебных пособиях автора по этой тематике. Учебное пособие предназначено для студентов бакалавриата и специалитета, изучающих дисциплину «Цифровая схемотехника». Может быть полезно для магистров и аспирантов.

УДК 681.399

ISBN 978-5-398-02397-8 |

© ПНИПУ, 2020 |

2

|

СОДЕРЖАНИЕ |

|

Введение............................................................................................ |

5 |

|

1. |

Логические элементы на основе транзисторов |

|

и их условные графические обозначения....................................... |

5 |

|

2. |

Моделирование логических элементов |

|

в системах схемотехнического моделирования............................. |

9 |

|

3. |

Уровни сигналов логических элементов.................................. |

10 |

4. |

Потребляемая мощность логических элементов ..................... |

12 |

5. |

Нагрузочная способность логических элементов |

|

(коэффициент разветвления) ......................................................... |

13 |

|

6. |

Быстродействие логических элементов ................................... |

13 |

7. |

Согласование уровней сигналов логических элементов. |

|

Преобразователи уровней.............................................................. |

15 |

|

8. |

Расширение местности логических операций ......................... |

16 |

9. |

Неиспользуемые входы, неиспользуемые элементы .............. |

17 |

10. Выходы биполярных элементов |

|

|

с открытым коллектором. Монтажная логика ............................. |

18 |

|

11. Элемент с тремя состояниями (Тристабильный буфер) ....... |

19 |

|

12. Одновентильные логические устройства ............................... |

22 |

|

13. Комбинационный автомат, комбинационная |

|

|

логика на транзисторном уровне .................................................. |

23 |

|

14. Задание комбинационного устройства |

|

|

в виде программы языка VHDL .................................................... |

30 |

|

|

14.1. Мультиплексор (Мультиплексор-селектор |

|

|

MS, MUX, MX) ........................................................................... |

31 |

|

14.2. Дешифратор ....................................................................... |

33 |

|

14.3. Кодер................................................................................... |

35 |

|

14.4. Нестандартный кодопреобразователь ............................. |

36 |

15. Последовательностная логика. |

|

|

Автомат-распознаватель 1011................................................................... |

36 |

|

|

15.1. Граф автомат-распознавателя 1011.................................. |

37 |

3

15.2. Получение логических функций |

|

автомата-распознавателя 1011 .................................................. |

41 |

15.3. Задание автомата-распознавателя 1011 |

|

на языке VHDL ........................................................................... |

48 |

16. Передача информации последовательным |

|

кодом с помощью регистров ......................................................... |

49 |

Список литературы......................................................................... |

52 |

4

ВВЕДЕНИЕ

Учебные пособия чем-то сродни несчетному множеству Кантора: любая попытка «уложить» материал в прокрустово ложе книг наталкивается на парадокс: всегда найдется тема, не вошедшая ни в одно учебное пособие. По крайней мере у автора. Нельзя объять необъятное…Тем не менее «Практическая цифровая схемотехника» – это n+1-я попытка дополнить уже имеющиеся пособия по цифровой схемотехнике, ибо очередное изменение учебных планов и их «цифровизация» как раз таки и предполагает расширение учебных часов по дисциплине. В то же время это очередная попытка согласования материала с другими, «смежными» учебными дисциплинами, рожденная в дискуссиях с О.В. Гончаровским, А.В. Гавриловым, В.И. Фрейманом и др. Причем упор сделан на описание обобщенных смыслов (семантики), а не конкретных деталей (синтаксиса). Предполагается, что учебное пособие будет доступно в электронном виде в библиотеке, поскольку опыт учебного процесса в «ковидный» период показал, что востребован именно такой формат литературы.

1.ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ НА ОСНОВЕ ТРАНЗИСТОРОВ

ИИХ УСЛОВНЫЕ ГРАФИЧЕСКИЕ ОБОЗНАЧЕНИЯ

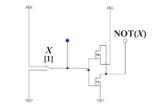

Простейший логический элемент – инвертор [12, 15, 21] выполняет простейшую логическую функцию отрицания (рис. 1):

Рис. 1. Модель КМОП – инвертора в системе схемотехнического моделирования Multisim [23]

5

Условные графические обозначения (УГО) в РФ выполняют по ГОСТ 2.743-91 [9]. Там инвертор почему-то называют элементом НЕТ (NOT по-английски – НЕ) (рис. 2).

Рис. 2. УГО элемента НЕТ (инвертор) по ГОСТ 2.743-91

Имеются также рекомендации международной электро-

технической комиссии IEC (International Electrotechnical Commission) (рис. 3).

а |

б |

Рис. 3. Международная электротехническая комиссия IEC:

а– логотип; б – здание центрального офиса в Женеве

Всоответствии с ними треугольное обозначение инвертора, принятое в системах схемотехнического моделирования, называется «традиционным» (distinctive shape, отличительная форма), а прямоугольное (как у нас – rectangular shape, прямоугольная форма) (рис. 4).

6

Рис. 4. Два варианта условного графического обозначения инвертора по IEC

В то же время допускается другой вид rectangular shape (рис. 5).

Рис. 5. Еще один вариант условного графического обозначения инвертора по IEC

То есть инверсия обозначается не кружком, а раздвоением линии. Похожие обозначения встречаются и в ГОСТ2.743-91, правда, для так называемого статического выхода с указателем полярности. Примеры УГО других логических элементов приведены на рис. 6.

7

Рис. 6. Примеры УГО двухвходовых логических элементов по IEC

На этих УГО нет обозначения входов питания. Так, Vcc по ГОСТ2.743-91 называется выводом питания от источника напряжения. Допускается обозначение U. Хотя само обозначение Vcc идет от коллекторного питания биполярных элементов, для МОП используют Vdd (drain – сток, иногда расшифровывают как digital device). Обозначение номеров элементов с аббревиатурой DD (digital device) показано на рис. 7

Рис. 7. Обозначение номеров элементов с аббревиатурой DD (digital device) с выводами питания

8

Общий вывод, земля, корпус по ГОСТ2.743-91 обозначается GND, хотя в нашем случае это ноль вольт, такое обозначение (0В) также допускает ГОСТ.

2.МОДЕЛИРОВАНИЕ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

ВСИСТЕМАХ СХЕМОТЕХНИЧЕСКОГО МОДЕЛИРОВАНИЯ

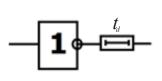

Логические элементы могут быть представлены простейшей дискретной моделью логической функции одной переменной с блоком задержки td на выходе, например для инвертора

(рис. 8).

Рис. 8. Модель инвертора с задержкой на выходе

Такая модель, несмотря на ее условность, применяется на практике [21]. Но она не учитывает динамики, того, что задержка меняется в зависимости от технологического разброса элементов, направления переключения (с 0 на 1 или с 1 на 0), зависимости от емкостной нагрузки и пр. Уточнение модели возможно путем использования в так называемом алфавите кроме 0 и 1 дополнительного символа Х, обозначающего неопределенное состояние в переходном процессе. Кроме этого используют символ Z (отключено, высокоимпедансное состояние), о котором речь идет дальше. Получают четырехсимвольный алфавит {0,1, Х, Z}. Кроме того, вводится понятие силы сигнала: слабый ноль L, слабая единица H, слабое неопределенное состояние W. Получают семь символов. Добавляют еще «не инициализировано» (U) и «не важно»(-), получается девятисимвольный алфавит в соответствии со стандартом IEEE 1164 [6] (рис. 9).

9

Рис. 9. Девятисимвольный алфавит моделирования цифровых устройств в соответствии

со стандартом IEEE 1164

Еще большее приближение к реальности дает аналоговое моделирование с использованием дифференциальных уравнений (как, например, в программе SPICE – Simulation Program with Integrated Circuit Emphasis). Но при этом резко увеличива-

ется объем вычислений, поэтому такой подход годится только для несложных элементов [21].

3. УРОВНИ СИГНАЛОВ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

При проектировании цифровых схем необходимо знать и учитывать статические и динамические параметры элементов. Прежде всего это напряжения и токи. Мы уже упоминали выше Vcc – напряжение питания (Vdd), GND (0В). Поскольку в цифровых элементах используются два уровня сигнала – 0 (Low) и 1 (High), то, очевидно, что Vcc – это 1, а GND (0В) – это 0. Напряжение питания имеет некоторый разброс (например 5 %), очевидно, разброс есть и для логических уровней, то есть необходимо определить, где «заканчивается» 0 и «начинается» 1 (диапазоны уровней напряжений логического 0 и логической 1).

10