- •16. ADVANCED LADDER LOGIC FUNCTIONS

- •16.1 INTRODUCTION

- •16.2 LIST FUNCTIONS

- •16.2.1 Shift Registers

- •16.2.2 Stacks

- •16.2.3 Sequencers

- •16.3 PROGRAM CONTROL

- •16.3.1 Branching and Looping

- •16.3.2 Fault Detection and Interrupts

- •16.4 INPUT AND OUTPUT FUNCTIONS

- •16.4.1 Immediate I/O Instructions

- •16.4.2 Block Transfer Functions

- •16.5 DESIGN TECHNIQUES

- •16.5.1 State Diagrams

- •16.6 DESIGN CASES

- •16.6.1 If-Then

- •16.6.2 Traffic Light

- •16.7 SUMMARY

- •16.8 PRACTICE PROBLEMS

- •16.9 PRACTICE PROBLEM SOLUTIONS

- •16.10 ASSIGNMENT PROBLEMS

- •17. OPEN CONTROLLERS

- •17.1 INTRODUCTION

- •17.3 OPEN ARCHITECTURE CONTROLLERS

- •17.4 SUMMARY

- •17.5 PRACTICE PROBLEMS

- •17.6 PRACTICE PROBLEM SOLUTIONS

- •17.7 ASSIGNMENT PROBLEMS

- •18. INSTRUCTION LIST PROGRAMMING

- •18.1 INTRODUCTION

- •18.2 THE IEC 61131 VERSION

- •18.3 THE ALLEN-BRADLEY VERSION

- •18.4 SUMMARY

- •18.5 PRACTICE PROBLEMS

- •18.6 PRACTICE PROBLEM SOLUTIONS

- •18.7 ASSIGNMENT PROBLEMS

- •19. STRUCTURED TEXT PROGRAMMING

- •19.1 INTRODUCTION

- •19.2 THE LANGUAGE

- •19.3 SUMMARY

- •19.4 PRACTICE PROBLEMS

- •19.5 PRACTICE PROBLEM SOLUTIONS

- •19.6 ASSIGNMENT PROBLEMS

- •20. SEQUENTIAL FUNCTION CHARTS

- •20.1 INTRODUCTION

- •20.2 A COMPARISON OF METHODS

- •20.3 SUMMARY

- •20.4 PRACTICE PROBLEMS

- •20.5 PRACTICE PROBLEM SOLUTIONS

- •20.6 ASSIGNMENT PROBLEMS

- •21. FUNCTION BLOCK PROGRAMMING

- •21.1 INTRODUCTION

- •21.2 CREATING FUNCTION BLOCKS

- •21.3 DESIGN CASE

- •21.4 SUMMARY

- •21.5 PRACTICE PROBLEMS

- •21.6 PRACTICE PROBLEM SOLUTIONS

- •21.7 ASSIGNMENT PROBLEMS

- •22. ANALOG INPUTS AND OUTPUTS

- •22.1 INTRODUCTION

- •22.2 ANALOG INPUTS

- •22.2.1 Analog Inputs With a PLC

- •22.3 ANALOG OUTPUTS

- •22.3.1 Analog Outputs With A PLC

- •22.3.2 Pulse Width Modulation (PWM) Outputs

- •22.3.3 Shielding

- •22.4 DESIGN CASES

- •22.4.1 Process Monitor

- •22.5 SUMMARY

- •22.6 PRACTICE PROBLEMS

- •22.7 PRACTICE PROBLEM SOLUTIONS

- •22.8 ASSIGNMENT PROBLEMS

- •23. CONTINUOUS SENSORS

- •23.1 INTRODUCTION

- •23.2 INDUSTRIAL SENSORS

- •23.2.1 Angular Displacement

- •23.2.1.1 - Potentiometers

- •23.2.2 Encoders

- •23.2.2.1 - Tachometers

- •23.2.3 Linear Position

- •23.2.3.1 - Potentiometers

- •23.2.3.2 - Linear Variable Differential Transformers (LVDT)

- •23.2.3.3 - Moire Fringes

- •23.2.3.4 - Accelerometers

- •23.2.4 Forces and Moments

- •23.2.4.1 - Strain Gages

- •23.2.4.2 - Piezoelectric

- •23.2.5 Liquids and Gases

- •23.2.5.1 - Pressure

- •23.2.5.2 - Venturi Valves

- •23.2.5.3 - Coriolis Flow Meter

- •23.2.5.4 - Magnetic Flow Meter

- •23.2.5.5 - Ultrasonic Flow Meter

- •23.2.5.6 - Vortex Flow Meter

- •23.2.5.7 - Positive Displacement Meters

- •23.2.5.8 - Pitot Tubes

- •23.2.6 Temperature

- •23.2.6.1 - Resistive Temperature Detectors (RTDs)

- •23.2.6.2 - Thermocouples

- •23.2.6.3 - Thermistors

- •23.2.6.4 - Other Sensors

- •23.2.7 Light

- •23.2.7.1 - Light Dependant Resistors (LDR)

- •23.2.8 Chemical

- •23.2.8.2 - Conductivity

- •23.2.9 Others

- •23.3 INPUT ISSUES

- •23.4 SENSOR GLOSSARY

- •23.5 SUMMARY

- •23.6 REFERENCES

- •23.7 PRACTICE PROBLEMS

- •23.8 PRACTICE PROBLEM SOLUTIONS

- •23.9 ASSIGNMENT PROBLEMS

- •24. CONTINUOUS ACTUATORS

- •24.1 INTRODUCTION

- •24.2 ELECTRIC MOTORS

- •24.2.1 Basic Brushed DC Motors

- •24.2.2 AC Motors

- •24.2.3 Brushless DC Motors

- •24.2.4 Stepper Motors

- •24.2.5 Wound Field Motors

plc basic functions - 15.35

5.A machine ejects parts into three chutes. Three optical sensors (A, B and C) are positioned in each of the slots to count the parts. The count should start when the reset (R) button is pushed. The count will stop, and an indicator light (L) turned on when the average number of parts counted equals 100.

6.Use an FAL instruction to average the values in N7:0 to N7:20 and store them in F8:0.

7.Write and simplify a Boolean equation that implements the masked move (MVM) instruction.

8.a) Write ladder logic to calculate and store the binary sequence in integer memory starting at N7:0 up to N7:200 so that N7:0 = 1, N7:1 = 2, N7:2 = 4, N7:3 = 8, N7:4 = 16, etc. b) Will the program operate as expected?

plc advanced functions - 16.1

16. ADVANCED LADDER LOGIC FUNCTIONS

Topics:

•Shift registers, stacks and sequencers

•Program control; branching, looping, subroutines, temporary ends and one shots

•Interrupts; timed, fault and input driven

•Immediate inputs and outputs

•Block transfer

•Conversion of State diagrams using program subroutines

•Design examples

Objectives:

•To understand shift registers, stacks and sequencers.

•To understand program control statements.

•To understand the use of interrupts.

•To understand the operation of immediate input and output instructions.

•To be prepared to use the block transfer instruction later.

•Be able to apply the advanced function in ladder logic design.

16.1INTRODUCTION

This chapter covers advanced functions, but this definition is somewhat arbitrary. The array functions in the last chapter could be classified as advanced functions. The functions in this section tend to do things that are not oriented to simple data values. The list functions will allow storage and recovery of bits and words. These functions are useful when implementing buffered and queued systems. The program control functions will do things that don’t follow the simple model of ladder logic execution - these functions recognize the program is executed left-to-right top-to-bottom. Finally, the input output functions will be discussed, and how they allow us to work around the normal input and output scans.

16.2LIST FUNCTIONS

16.2.1Shift Registers

Shift registers are oriented to single data bits. A shift register can only hold so many bits, so when a new bit is put in, one must be removed. An example of a shift regis-

plc advanced functions - 16.2

ter is given in Figure 16.1. The shift register is the word B3:1, and it is 5 bits long. When A becomes true the bits all shift right to the least significant bit. When they shift a new bit is needed, and it is taken from I:000/0. The bit that is shifted out, on the right hand side, is moved to the control word UL (unload) bit R6:2/UL. This function will not complete in a single ladder logic scan, so the control word R6:2 is used. The function is edge triggered, so A would have to turn on 5 more times before the bit just loaded from I:000/0 would emerge to the unload bit. When A has a positive edge the bits in B3:1 will be shifted in memory. In this case it is taking the value of bit B3:1/0 and putting it in the control word bit R6:2/UL. It then shifts the bits once to the right, B3:1/0 = B3:1/1 then B3:1/1 = B3:1/2 then B3:1/2 = B3:1/3 then B3:1/3 = B3:1/4. Then the input bit is put into the most significant bit B3:1/4 = I:000/00. The bits in the shift register can also be shifted to the left with the BSL function.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

bits shift right |

|||||

B3:1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

MSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSB |

|||

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|||||||

|

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

00 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

I:000/00 |

|

|

|

|

R6:2/UL |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

5 |

|

|

|

|||||||||

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BSR |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

File B3:1 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Control R6:2 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit address I:000/00 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Length 5 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BSL - shifts left from the LSB to the MSB. The LSB must be supplied

BSR - similar to the BSL, except the bit is input to the MSB and shifted to the LSB

Figure 16.1 Shift Register Functions

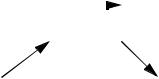

There are other types of shift registers not implemented in PLC-5s. These are shown in Figure 16.2. The primary difference is that the arithmetic shifts will put a zero into the shift register, instead of allowing an arbitrary bit. The rotate functions shift bits around in an endless circle. These functions can also be implemented using the BSR and BSL instructions when needed.

plc advanced functions - 16.3

Arithmetic Shift Left (ASL) |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

carry |

msb |

|

|

|

|

|

|

|

|

lsb |

|

|

|

|||

|

0 |

|

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

|

||

|

|

|

|

|

|

|

|||||||||||

Arithmetic Shift Right (ASR) |

|

|

|

|

|

|

|

|

|

|

|

carry |

|||||

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

||||||||

|

|

|

0 |

|

|||||||||||||

Rotate Left (ROL) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

carry |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

Rotate Right (ROR) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||||||||

carry

0

0

Figure 16.2 Shift Register Variations

16.2.2 Stacks

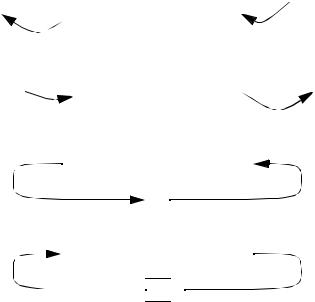

Stacks store integer words in a two ended buffer. There are two basic types of stacks; first-on-first-out (FIFO) and last-in-first-out (LIFO). As words are pushed on the stack it gets larger, when words are pulled off it gets smaller. When you retrieve a word from a LIFO stack you get the word that is the entry end of the stack. But, when you get a word from a FIFO stack you get the word from the exit end of the stack (it has also been there the longest). A useful analogy is a pile of work on your desk. As new work arrives you drop it on the top of the stack. If your stack is LIFO, you pick your next job from the top of the pile. If your stack is FIFO, you pick your work from the bottom of the pile. Stacks are very helpful when dealing with practical situations such as buffers in production lines. If the buffer is only a delay then a FIFO stack will keep the data in order. If product is buffered by piling it up then a LIFO stack works better, as shown in Figure 16.3. In a FIFO stack the parts pass through an entry gate, but are stopped by the exit gate. In the LIFO stack the parts enter the stack and lower the plate, when more parts are needed the plate is raised. In this arrangement the order of the parts in the stack will be reversed.

plc advanced functions - 16.4

entry gate |

exit gate |

FIFO |

|

LIFO

Figure 16.3 Buffers and Stack Types

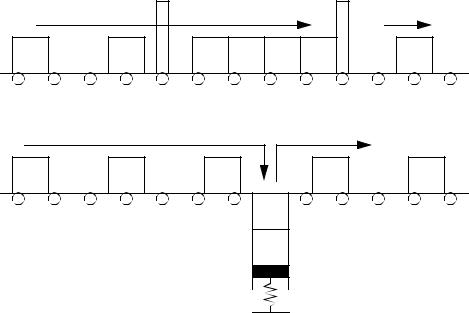

The ladder logic functions are FFL to load the stack, and FFU to unload it. The example in Figure 16.4 shows two instructions to load and unload a FIFO stack. The first time this FFL is activated (edge triggered) it will grab the word (16 bits) from the input card I:001 and store them on the stack, at N7:0. The next value would be stored at N7:1, and so on until the stack length is reached at N7:4. When the FFU is activated the word at N7:0 will be moved to the output card O:003. The values on the stack will be shifted up so that the value previously in N7:1 moves to N7:0, N7:2 moves to N7:1, etc. If the stack is full or empty, an a load or unload occurs the error bit will be set R6:0/ER.

plc advanced functions - 16.5

A

FFL

source I:001 FIFO N7:0 Control R6:0 length 5 position 0

B

FFU

FIFO N7:0 destination O:003 Control R6:0 length 5

position 0

Figure 16.4 FIFO Stack Instructions

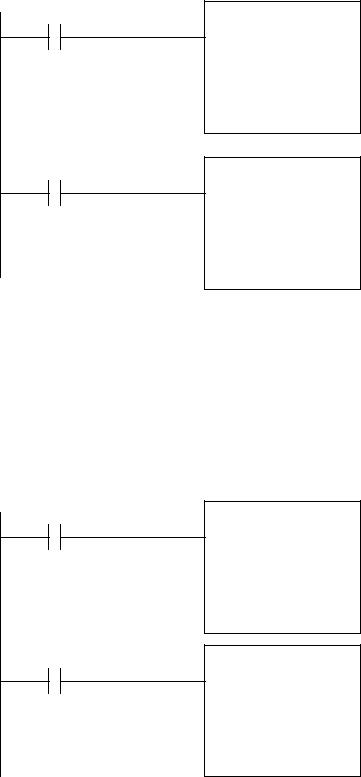

The LIFO stack commands are shown in Figure 16.5. As values are loaded on the stack the will be added sequentially N7:0, N7:1, N7:2, N7:3 then N7:4. When values are unloaded they will be taken from the last loaded position, so if the stack is full the value of N7:4 will be removed first.

A

LFL

source I:001 LIFO N7:0 Control R6:0 length 5 position 0

B

LFU

LIFO N7:0 destination O:003 Control R6:0 length 5

position 0

Figure 16.5 LIFO Stack Commands